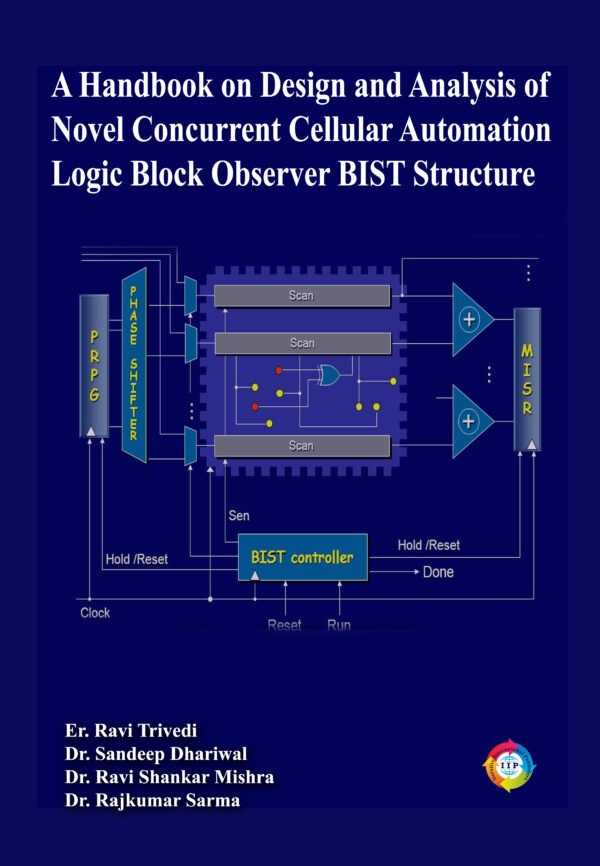

An efficient Design for Testability (DFT) has been a major concern for today’s VLSI engineers. A poorly designed DFT would result in losses for manufacturers with a considerable rework for the designers. Built-in Self-Test (BIST) – One of the promising DFT techniques is rapidly modifying with the advances in technology as device shrinks. Because of the growing complexities of the hardware, the trend has shifted to include BISTs in high performance circuitry for offline as well as online testing. Work done here involves testing various Circuit Under Test (CUT) with different techniques of built in response analyzer and vector generator with a monitor to control all the activities. Use of low transition vector generators like Bit-Swapping Complete Feedback Shift Register (BS-CFSR), Cellular Automata Registers (CAR), Concurrent Built-In Logic Block Observer (CBILBO), and, novel design Concurrent Cellular Automata Logic Block Observer (CCALBO) an effort is made to reduce power consumption by comparing it to classical Linear Feedback Shift Register (LFSR) techniques. This book presents the process of design implementation for a complete BIST working on both normal operation mode as well as test mode for multiple circuitry like Carry Look Ahead (CLA) adder, ISCAS benchmark circuits (74XX series) – 74181 and 74283, Vedic Multiplier, and Multiply and Accumulate processor. A thorough comparison is carried out by comparing all the DFT techniques with each other. Xilinx Vivado 2018.1 for coding in Verilog and implementation with Cadence’s Encounter(R) RTL Compiler RC 14.10 were used for timing responses, area calculations, and power consumption at different technology nodes.

Sale

₹380.00 Original price was: ₹380.00.₹304.00Current price is: ₹304.00. ₹

₹1,200.00 Original price was: ₹1,200.00.₹960.00Current price is: ₹960.00. ₹

₹699.00 Original price was: ₹699.00.₹559.20Current price is: ₹559.20. ₹

₹590.00 Original price was: ₹590.00.₹472.00Current price is: ₹472.00. ₹

₹450.00 Original price was: ₹450.00.₹360.00Current price is: ₹360.00. ₹

₹350.00 Original price was: ₹350.00.₹280.00Current price is: ₹280.00. ₹

₹200.00 Original price was: ₹200.00.₹160.00Current price is: ₹160.00. ₹

” A HANDBOOK ON DESIGN AND ANALYSIS OF NOVEL CONCURRENT CELLULAR AUTOMATION LOGIC BLOCK OBSERVER BIST STRUCTURE”

Er. Ravi Trivedi, Dr. Rajkumar Sarma, Dr. Ravi Shankar Mishra, Dr. Sandeep Dhariwal 978-1-68576-081-6

FIRST

ACADEMIC, PhD Thesis/Thesis, Physics

Meet The Author

No products were found matching your selection.

No products were found matching your selection.

No products were found matching your selection.

Be the first to review “” A HANDBOOK ON DESIGN AND ANALYSIS OF NOVEL CONCURRENT CELLULAR AUTOMATION LOGIC BLOCK OBSERVER BIST STRUCTURE”” Cancel reply

Reviews

There are no reviews yet.